[solved] . to build a 4-to-1 mux using only 2-to-1 muxes, how many Mux multiplexer verilog 4x2 2x1 muxes block low Multiplexer (mux)

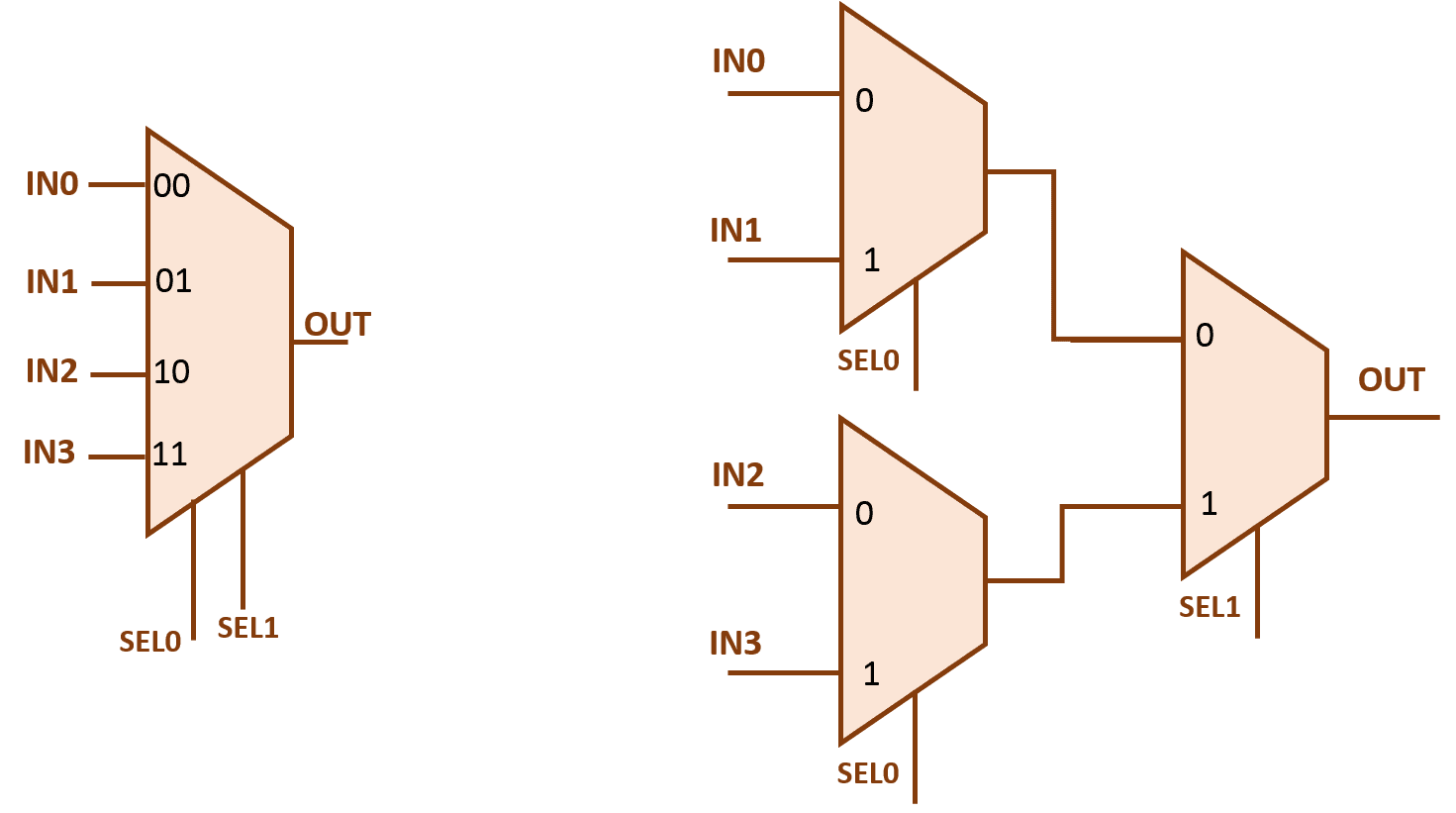

[Solved] . To build a 4-to-1 MUX using only 2-to-1 MUXes, how many

Multiplexores en lógica digital – acervo lima

Mux multiplexer cascading multiplexing techniques

Design 16*1 mux using 2*1 muxMultiplexer inputs What is a multiplexer? operation, types and applicationsMultiplexeurs en logique numérique – stacklima.

Multiplexer and demultiplexer circuit diagramMux logic multiplexer vhdl gates allaboutfpga Imx6ull的iomux配置方法_mux寄存器-csdn博客Full custom ic(5).

2x1 mux multiplexer diagram logic schematic using figure symbol gates input

2 1 mux circuit diagramTransistor level implementation of 2:1 mux using custom compiler tool Function syntax in verilog(4:1 mux implementation using 2:1 mux)Implement 8:1 mux using 4:1 mux.

Mux logicMux 4x1 vlsi eda Design 16*1 mux using 2*1 muxMux using digital 16 multiplexers implement electronics general geeksforgeeks formula same used.

3 to 1 mux

Vhdl 4 to 1 mux (multiplexer)Design and implement 8:1 multiplexer Multiplexer 1) a) using 4:1 mux only, make 28:1 mux b) using 8:1Dwdm mux/demux 50ghz 96ch (c15-c62) 2u rack.

Digital logicVerilog: mux 2 to 1 (multiplexer) Multiplexer mux demultiplexer d0 d3 d1 d2 pptTruth table for logic gates with 4 inputs – two birds home.

Design of 4×2 multiplexer using 2×1 mux in verilog

Vhdl multiplexer mux2*1 multiplexer circuit diagram / 2 1 mux using cmos logic multisim Mux multisimVerilog: mux 2 to 1 (multiplexer).

.